האירופה הראתה כיצד לפתח מעבד שרת משלה על בסיס RISC‑V בתהליך של אינטל 3

הפחתת התלות בייבוא באירופה: ניסוי חדש עם RISC‑V

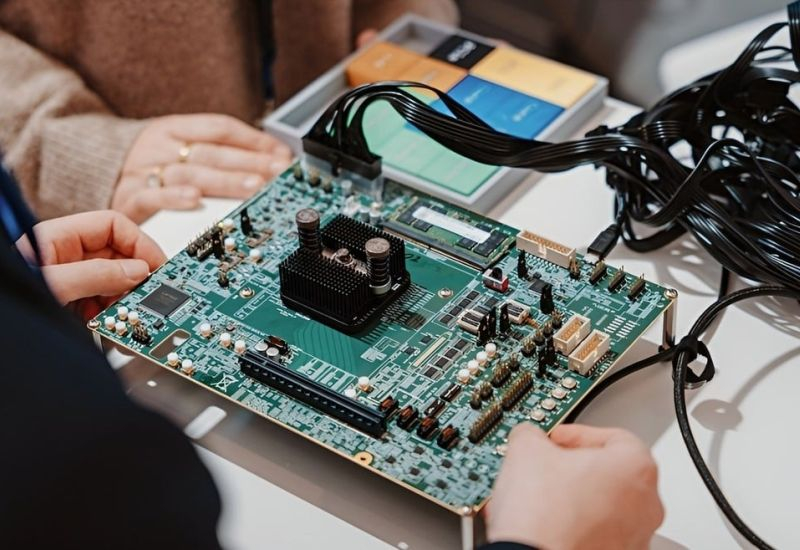

מהנדסי אירופה ממרכז החישוב העליון של ברצלונה (BSC‑CNS) אישרו כי מעבדי השרת שלהם TC1 מבוססי הארכיטקטורה הפתוחה RISC‑V פועלים כראוי. המעבדים מיוצרים בטכנולוגיית Intel 3, מה שמאפשר להם לצאת מתלות בשרשרות אספקה אסיאתיות ובפלטפורמות פרטיות.

מה נעשה

- המטרה – ליצור שבב שרתי, בלתי תלוי במפיקים גדולים (Intel, AMD) וללא TSMC תאיואני.

- הביצוע – המפתחים החליפו את התלות אחת בתלויה אחרת: במקום לייצר מעבדים בעצמם, הם הזמינו חבילת ניסוי מ‑Intel.

פרטי טכניקה

המשתנה | ערך | פרטים טכניים

טכנולוגיית תהליך | Intel 3 (לא מהמתקדמות אך מתאימה לפרויקטים קטנים) | גודל הלחם 15,2 מ״ק²

שטח ליבת ה‑CPU | 3,2 מ״ק²

תדירות | עד 1,25 GHz (נעלה מההצהרה)

תמיכה בממשקים | PCI Express 5.0, DDR5

רכיבים | ארכיטקטורה שלושה חלקים: *Sargantana*, *Lagarto Ka* ו-*Lagarto Ox*

ב‑מאי של השנה שעברה, הדגימות הראשונות של TC1 אפשרו כבר להעלות לינוקס על פלטפורמת Intel Hawk Canyon V2.

למה זה חשוב

- התלות בייבוא – המפתחים האירופיים צריכים לצמצם את התלות במתן אמריקאי ואסייתי.

- כלכלה – הזמנת חבילות קטנות מ‑Intel יכולה לשפר את מצבה הפיננסי של החברה, ולהדגים את יישום הטכנולוגיות האלטרנטיביות.

- סקלה – BSC‑CNS לא מתכנן ייצור מסחרי, אך הניסוי מעיד שהרעיון אפשרי.

סיכום

מעבדי TC1 מוכיחים כי הארכיטקטורה הפתוחה RISC‑V והפתרונות הטכנולוגיים הזמינים מאפשרים לחברות אירופיות לפתח תשתית קריטית משלהן ללא תלות בקורפראציות גדולות. זה יכול להיות נקודת התחלה לנסיונות נוספים להוציא שבבים לשוק ולחזק את העצמאות מהשרשרות האספקה החיצוניות.

Asted Cloud

Asted Cloud

תגובות (0)

שתפו את דעתכם — אנא היו מנומסים והישארו בנושא.

התחברו כדי להגיב